ಡಿ-ಎಫ್ಇಟಿಯು 0 ಗೇಟ್ ಬಯಾಸ್ನಲ್ಲಿದ್ದರೆ, ಚಾನಲ್ನ ಅಸ್ತಿತ್ವವು FET ಅನ್ನು ನಡೆಸಬಹುದು; ಯಾವುದೇ ಚಾನಲ್ ಇಲ್ಲದಿದ್ದಾಗ E-FET 0 ಗೇಟ್ ಪಕ್ಷಪಾತದಲ್ಲಿದೆ, FET ಅನ್ನು ನಡೆಸಲು ಸಾಧ್ಯವಿಲ್ಲ. ಈ ಎರಡು ರೀತಿಯ FET ಗಳು ತಮ್ಮದೇ ಆದ ಗುಣಲಕ್ಷಣಗಳನ್ನು ಮತ್ತು ಉಪಯೋಗಗಳನ್ನು ಹೊಂದಿವೆ. ಸಾಮಾನ್ಯವಾಗಿ, ಹೆಚ್ಚಿನ ವೇಗದ, ಕಡಿಮೆ-ವಿದ್ಯುತ್ ಸರ್ಕ್ಯೂಟ್ಗಳಲ್ಲಿ ವರ್ಧಿತ FET ಬಹಳ ಮೌಲ್ಯಯುತವಾಗಿದೆ; ಮತ್ತು ಈ ಸಾಧನವು ಕಾರ್ಯನಿರ್ವಹಿಸುತ್ತಿದೆ, ಇದು ಗೇಟ್ ಬಯಾಸ್ vo ನ ಧ್ರುವೀಯತೆಯಾಗಿದೆltage ಮತ್ತು ಡ್ರೈನ್ ಅದೇ ವೋಲ್ಟೇಜ್, ಇದು ಸರ್ಕ್ಯೂಟ್ ವಿನ್ಯಾಸದಲ್ಲಿ ಹೆಚ್ಚು ಅನುಕೂಲಕರವಾಗಿದೆ.

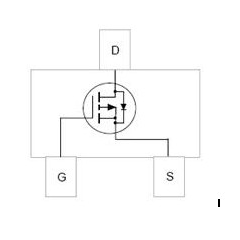

ವರ್ಧಿತ ವಿಧಾನಗಳೆಂದು ಕರೆಯಲ್ಪಡುವ: VGS = 0 ಟ್ಯೂಬ್ ಒಂದು ಕಟ್-ಆಫ್ ಸ್ಥಿತಿ, ಜೊತೆಗೆ ಸರಿಯಾದ VGS ಆಗಿರುವಾಗ, ಹೆಚ್ಚಿನ ವಾಹಕಗಳು ಗೇಟ್ಗೆ ಆಕರ್ಷಿತವಾಗುತ್ತವೆ, ಹೀಗಾಗಿ ಪ್ರದೇಶದ ವಾಹಕಗಳನ್ನು "ಹೆಚ್ಚಿಸುತ್ತದೆ", ವಾಹಕ ಚಾನಲ್ ಅನ್ನು ರೂಪಿಸುತ್ತದೆ. n-ಚಾನೆಲ್ ವರ್ಧಿತ MOSFET ಮೂಲತಃ ಎಡ-ಬಲ ಸಮ್ಮಿತೀಯ ಟೋಪೋಲಜಿಯಾಗಿದೆ, ಇದು SiO2 ಫಿಲ್ಮ್ ಇನ್ಸುಲೇಶನ್ನ ಪದರದ ಪೀಳಿಗೆಯ ಮೇಲೆ P-ಟೈಪ್ ಸೆಮಿಕಂಡಕ್ಟರ್ ಆಗಿದೆ. ಇದು ಪಿ-ಟೈಪ್ ಸೆಮಿಕಂಡಕ್ಟರ್ನಲ್ಲಿ SiO2 ಫಿಲ್ಮ್ನ ನಿರೋಧಕ ಪದರವನ್ನು ಉತ್ಪಾದಿಸುತ್ತದೆ ಮತ್ತು ನಂತರ ಎರಡು ಹೆಚ್ಚು ಡೋಪ್ಡ್ N- ಪ್ರಕಾರದ ಪ್ರದೇಶಗಳನ್ನು ಹರಡುತ್ತದೆಫೋಟೋಲಿಥೋಗ್ರಫಿ, ಮತ್ತು N-ಮಾದರಿಯ ಪ್ರದೇಶದಿಂದ ಎಲೆಕ್ಟ್ರೋಡ್ಗಳನ್ನು ಮುನ್ನಡೆಸುತ್ತದೆ, ಡ್ರೈನ್ D ಗಾಗಿ ಒಂದು ಮತ್ತು ಮೂಲ S ಗಾಗಿ ಒಂದು ಅಲ್ಯೂಮಿನಿಯಂ ಲೋಹದ ಪದರವು ಮೂಲ ಮತ್ತು ಡ್ರೈನ್ ನಡುವಿನ ನಿರೋಧಕ ಪದರದ ಮೇಲೆ ಗೇಟ್ G ಆಗಿ ಲೇಪಿತವಾಗಿದೆ. VGS = 0 V , ಡ್ರೈನ್ ಮತ್ತು ಮೂಲದ ನಡುವೆ ಬ್ಯಾಕ್-ಟು-ಬ್ಯಾಕ್ ಡಯೋಡ್ಗಳೊಂದಿಗೆ ಕೆಲವು ಡಯೋಡ್ಗಳಿವೆ ಮತ್ತು D ಮತ್ತು S ನಡುವಿನ ವೋಲ್ಟೇಜ್ D ಮತ್ತು S ನಡುವೆ ಪ್ರವಾಹವನ್ನು ರೂಪಿಸುವುದಿಲ್ಲ. D ಮತ್ತು S ನಡುವಿನ ಪ್ರಸ್ತುತವು ಅನ್ವಯಿಸಲಾದ ವೋಲ್ಟೇಜ್ನಿಂದ ರೂಪುಗೊಂಡಿಲ್ಲ.

ಗೇಟ್ ವೋಲ್ಟೇಜ್ ಅನ್ನು ಸೇರಿಸಿದಾಗ, 0 < VGS < VGS(th), ಗೇಟ್ ಮತ್ತು ತಲಾಧಾರದ ನಡುವೆ ರೂಪುಗೊಂಡ ಕೆಪ್ಯಾಸಿಟಿವ್ ವಿದ್ಯುತ್ ಕ್ಷೇತ್ರದ ಮೂಲಕ, ಗೇಟ್ನ ಕೆಳಭಾಗದಲ್ಲಿರುವ P-ಟೈಪ್ ಸೆಮಿಕಂಡಕ್ಟರ್ನಲ್ಲಿರುವ ಪಾಲಿಯಾನ್ ರಂಧ್ರಗಳನ್ನು ಕೆಳಕ್ಕೆ ಹಿಮ್ಮೆಟ್ಟಿಸಲಾಗುತ್ತದೆ ಮತ್ತು ನಕಾರಾತ್ಮಕ ಅಯಾನುಗಳ ತೆಳುವಾದ ಸವಕಳಿ ಪದರವು ಕಾಣಿಸಿಕೊಳ್ಳುತ್ತದೆ; ಅದೇ ಸಮಯದಲ್ಲಿ, ಇದು ಮೇಲ್ಮೈ ಪದರಕ್ಕೆ ಚಲಿಸಲು ಅದರಲ್ಲಿರುವ ಆಲಿಗಾನ್ಗಳನ್ನು ಆಕರ್ಷಿಸುತ್ತದೆ, ಆದರೆ ಡ್ರೈನ್ ಮತ್ತು ಮೂಲವನ್ನು ಸಂವಹನ ಮಾಡುವ ವಾಹಕ ಚಾನಲ್ ಅನ್ನು ರೂಪಿಸಲು ಸಂಖ್ಯೆ ಸೀಮಿತವಾಗಿದೆ ಮತ್ತು ಸಾಕಾಗುವುದಿಲ್ಲ, ಆದ್ದರಿಂದ ಡ್ರೈನ್ ಕರೆಂಟ್ ಐಡಿ ರಚನೆಗೆ ಇದು ಇನ್ನೂ ಸಾಕಾಗುವುದಿಲ್ಲ. ಮತ್ತಷ್ಟು ಹೆಚ್ಚಳ ವಿಜಿಎಸ್, ಯಾವಾಗ ವಿಜಿಎಸ್ > VGS (th) (VGS (th) ಅನ್ನು ಟರ್ನ್-ಆನ್ ವೋಲ್ಟೇಜ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ), ಏಕೆಂದರೆ ಈ ಸಮಯದಲ್ಲಿ ಗೇಟ್ ವೋಲ್ಟೇಜ್ ತುಲನಾತ್ಮಕವಾಗಿ ಪ್ರಬಲವಾಗಿದೆ, P- ಮಾದರಿಯ ಸೆಮಿಕಂಡಕ್ಟರ್ ಮೇಲ್ಮೈ ಪದರದಲ್ಲಿ ಗೇಟ್ನ ಕೆಳಭಾಗದಲ್ಲಿ ಹೆಚ್ಚು ಒಟ್ಟುಗೂಡಿಸುತ್ತದೆ ಎಲೆಕ್ಟ್ರಾನ್ಗಳು, ನೀವು ಕಂದಕ, ಡ್ರೈನ್ ಮತ್ತು ಸಂವಹನದ ಮೂಲವನ್ನು ರಚಿಸಬಹುದು. ಈ ಸಮಯದಲ್ಲಿ ಡ್ರೈನ್ ಮೂಲ ವೋಲ್ಟೇಜ್ ಅನ್ನು ಸೇರಿಸಿದರೆ, ಡ್ರೈನ್ ಕರೆಂಟ್ ಅನ್ನು ಐಡಿ ರಚಿಸಬಹುದು. ಗೇಟ್ನ ಕೆಳಗೆ ರೂಪುಗೊಂಡ ವಾಹಕ ಚಾನಲ್ನಲ್ಲಿನ ಎಲೆಕ್ಟ್ರಾನ್ಗಳು, ಪಿ-ಟೈಪ್ ಸೆಮಿಕಂಡಕ್ಟರ್ ಧ್ರುವೀಯತೆಯೊಂದಿಗೆ ವಾಹಕ ರಂಧ್ರವು ವಿರುದ್ಧವಾಗಿರುತ್ತದೆ, ಆದ್ದರಿಂದ ಇದನ್ನು ಆಂಟಿಟೈಪ್ ಲೇಯರ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ. VGS ಹೆಚ್ಚುತ್ತಿರುವಂತೆ, ID ಹೆಚ್ಚಾಗುತ್ತಲೇ ಇರುತ್ತದೆ. VGS = 0V ನಲ್ಲಿ ID = 0, ಮತ್ತು ಡ್ರೈನ್ ಕರೆಂಟ್ VGS > VGS (th) ನಂತರ ಮಾತ್ರ ಸಂಭವಿಸುತ್ತದೆ, ಆದ್ದರಿಂದ, ಈ ರೀತಿಯ MOSFET ಅನ್ನು ವರ್ಧನೆ MOSFET ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ.

ಡ್ರೈನ್ ಕರೆಂಟ್ ಮೇಲೆ VGS ನ ನಿಯಂತ್ರಣ ಸಂಬಂಧವನ್ನು ವಕ್ರರೇಖೆಯಿಂದ ವಿವರಿಸಬಹುದು iD = f(VGS(th))|VDS=const, ಇದನ್ನು ವರ್ಗಾವಣೆ ವಿಶಿಷ್ಟ ಕರ್ವ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ, ಮತ್ತು ವರ್ಗಾವಣೆ ವಿಶಿಷ್ಟ ಕರ್ವ್ನ ಇಳಿಜಾರಿನ ಪ್ರಮಾಣ, gm, ಗೇಟ್ ಮೂಲ ವೋಲ್ಟೇಜ್ನಿಂದ ಡ್ರೈನ್ ಪ್ರವಾಹದ ನಿಯಂತ್ರಣವನ್ನು ಪ್ರತಿಬಿಂಬಿಸುತ್ತದೆ. gm ನ ಪ್ರಮಾಣವು mA/V ಆಗಿರುತ್ತದೆ, ಆದ್ದರಿಂದ gm ಅನ್ನು ಟ್ರಾನ್ಸ್ಕಂಡಕ್ಟನ್ಸ್ ಎಂದೂ ಕರೆಯುತ್ತಾರೆ.